IPrium releases BCH Encoder and Decoder

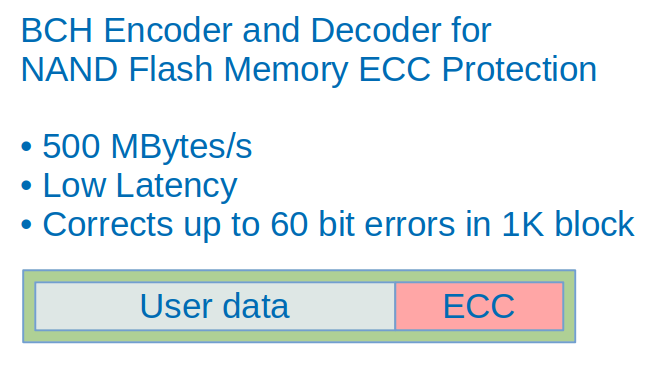

FOGGIA, Italy, November 05, 2024 - FPGA intellectual property (IP) provider IPrium LLC (www.iprium.com) has today announced that it has expanded its family of FEC Encoder and Decoder IP products with a new BCH Codec.

The BCH Codec IP Core supports a wide range of code block and payload sizes up to 8191 bytes with high error correction performance. The IP Core is customizable to any standard, including NAND Flash Memory and DVB.

Pricing and Availability

The BCH Encoder and Decoder IP Core is available immediately in synthesizable Verilog or optimized netlist format, along with synthesis scripts, simulation test bench with expected results, and user manual. For further information, a product evaluation or pricing, please visit the IP Core page:

About IPrium LLC

IPrium Modem IP Cores allow designers of communication equipment to rapidly develop and verify their systems in a highly cost-effective manner. IPrium offers FPGA IP Cores for high-quality wireless and wireline modems. Visit IPrium at www.iprium.com.

return